Жерихов Егор Петрович

студент

ФГАОУ ВО «Национальный исследовательский университет

«Московский институт электронной техники»

г. Зеленоград, Московская область

## МЕТОДЫ УМЕНЬШЕНИЯ ЭНЕРГОПОТРЕБЛЕНИЯ КМОП БИС

*Аннотация:* в последнее время в современном мире микроэлектроники прослеживаются две ключевые тенденции: увеличение быстродействия и снижение энергопотребления. Создание электронных устройств с большей вычислительной мощностью и малым энергопотреблением, позволяет нам использовать более компактные приборы, работающие на аккумуляторах или батареях. Тенденция разработки новых приложений, программ и ПО неуклонно растет, тем самым удовлетворяя желания потребителей, а между тем различные инновации и нововведения требуют все больше энергии, тем самым уменьшая время работы портативных устройств. Как пример мы можем сравнить время работы мобильного телефона в 2000 году и в 2014 году, или же время работы современных смартфонов на различных операционных системах. Развитие старых и разработка новых методов снижения энергопотребления – актуальные темы для исследования в мире микроэлектроники, поскольку чем энергоэкономичнее будут современные приборы, тем дольше и быстрее они смогут работать.

*Ключевые слова:* уменьшение энергопотребления, КМОП структура, FinFET технология, VTCMOS технология.

На данный момент не найдено универсальное решение, которое решило бы данную проблему во всех возможных ситуациях. По этой причине нужно учитывать особенности проектируемых устройств, такие как быстродействие, надежность, затраты на создание и т.п.

Рассмотрим основные методы, которые могут использоваться комплексно или в отдельности для уменьшения энергопотребления при проектировании КМОП БИС.

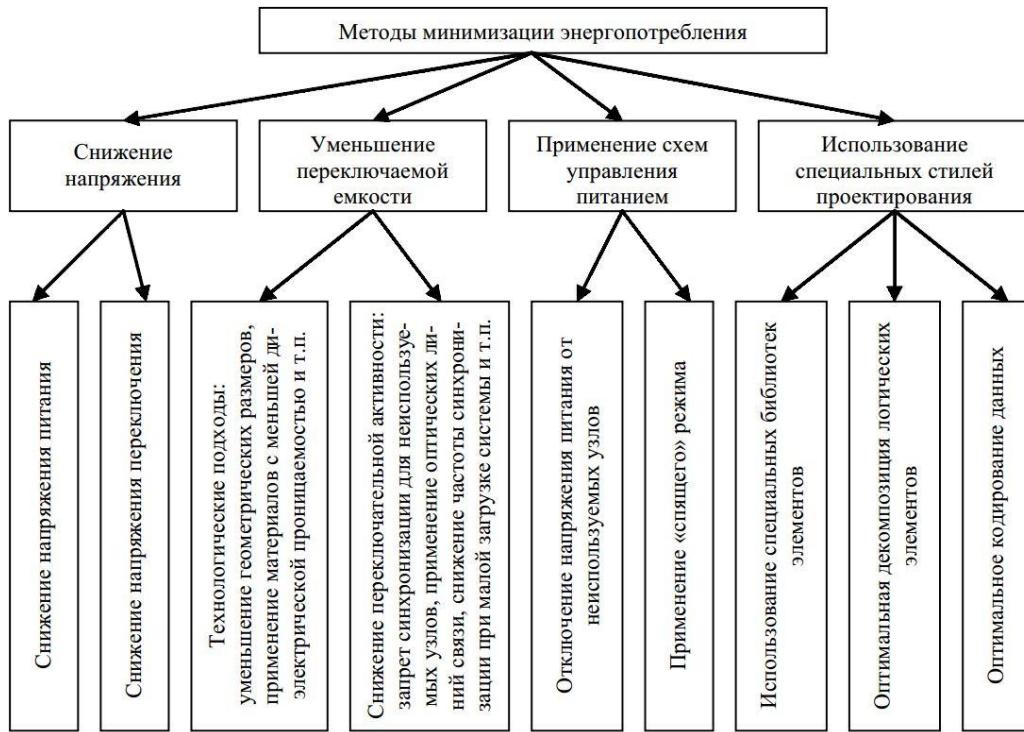

Рис. 1. Классификация методов минимизации энергопотребления при проектировании КМОП БИС

На рисунке 1 представлена обобщенная классификация основных используемых методов минимизации энергопотребления. При традиционных КМОП-технологиях (минимальные размеры элементов не переходят в субмикронную область) основную долю рассеиваемой мощности составляет динамическая мощность. Снижение любого параметра: напряжения питания, напряжения переключения, перезаряжаемой емкости или частоты переключения- приводит к уменьшению величины рассеиваемой мощности.

Обычно наибольшее внимание инженеров направлено на уменьшение величины напряжения питания. Это связано с тем, что для большинства КМОП БИС напряжение питания равно напряжению переключения. Между динамической рассеиваемой мощностью и напряжением питания ИС существует квадратичная зависимость. Помимо этого, при уменьшении напряжения питания одновременно уменьшается и статическая мощность.

При анализе энергопотребления КМОП БИС выделяют две основные составляющие энергопотребления: статическая и динамическая. Статическая составляющая включает в себя следующие различные компоненты: токи связанные

с туннелированием, токи утечек через р-п переходы, подпороговые токи утечки. К динамической составляющей относятся следующие эффекты: перезарядка емкостей схемы и сквозные токи в процессе переключения узлов схемы. Общее потребление КМОП СБИС можно представить в виде следующего выражения:

$$P = C_L \cdot V_{dd}^2 \cdot \alpha_T \cdot f + V_{dd} \cdot I_{sc} + V_{dd} \cdot I_{leak}, \quad (1)$$

где  $P$  – общая потребляемая мощность,  $C_L$  – нагрузочная емкость,  $V_{dd}$  – напряжение питания,  $\alpha_T$  – активность переключений,  $f$  – тактовая частота,  $I_{sc}$  – сквозной ток,  $I_{leak}$  – суммарный ток утечки.

Следующим фактором, влияющим на величину динамической мощности, является частота переключения, поэтому ее снижение также будет приводить к снижению рассеиваемой мощности. Однако при этом возникает конфликт с требованиями, касающимися производительности. Для устранения этого конфликта можно использовать различные подходы. Во-первых, при проектировании новых устройств приоритет должен отдаваться решениям с пониженными требованиями к рабочей частоте функциональных компонентов. Во-вторых, для снижения тактовой частоты необходимо применять методы параллельного выполнения операций на конвейере. В-третьих, целесообразно использовать различные схемы запрета синхронизации как для неиспользуемых функциональных модулей, так и для модулей или компонентов, информация в которых не изменяется в данный момент. Например, при проведении целочисленных вычислений обычно не используются узлы сопроцессора, которые предназначены для вычислений с плавающей запятой, поэтому на эти узлы в данный момент импульсы синхронизации поступать не должны.

#### *Снижение энергопотребления на технологическом уровне*

В современных технологиях, начиная с уровня 0,18 мкм КМОП, имеется возможность изготовления МОП-транзистора с двумя значениями порогового напряжения, что обеспечивает совместимость с методом множественных пороговых напряжений на функционально-логическом уровне.

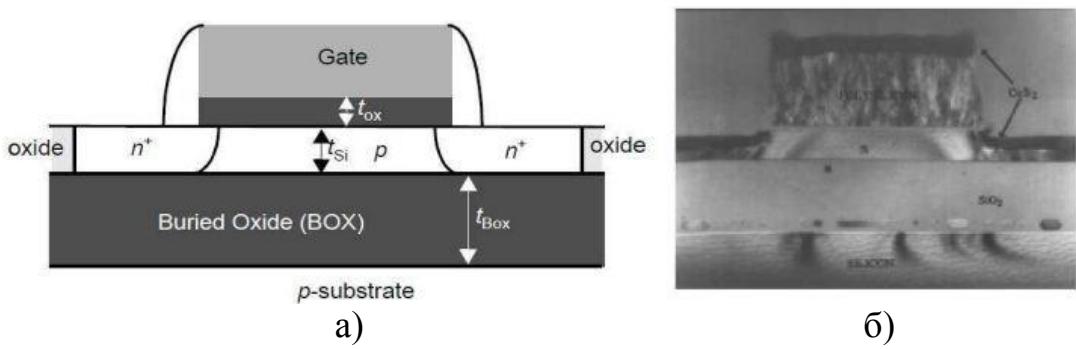

В настоящее время все более широко применяется технология Silicon-on-insulator (SOI). Структура МОП-транзистора, изготовленного по технологии SOI приведена на рисунке 2.

Рис. 2. Структура КМОП SOI: а) схематическое изображение структуры транзистора; б) полученный с помощью сканирующего электронного микроскопа вид поперечного сечения

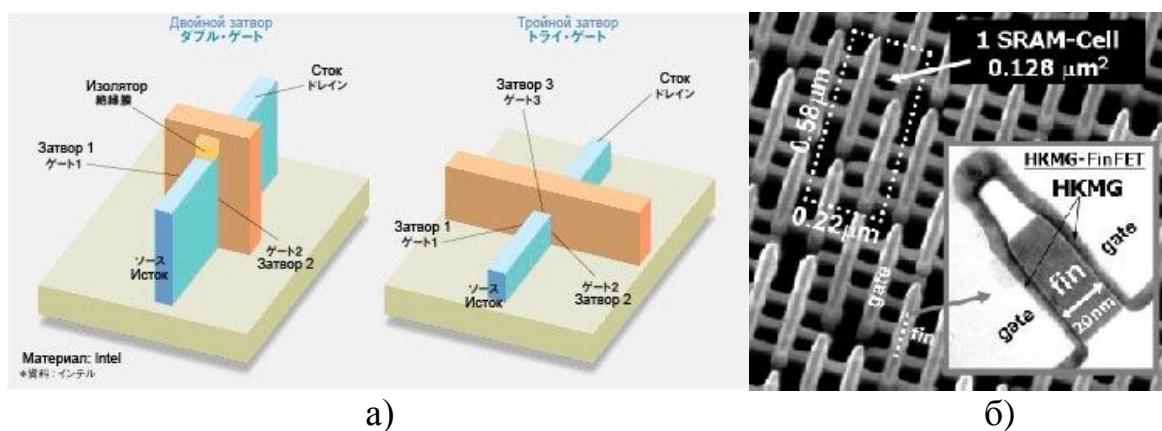

За счет уменьшения емкостей SOI МОП-транзистора удается уменьшить потребляемую мощность, задержки и занимаемую площадь. При переходе к наноразмерным топологическим нормам также успешно используются технологии на объемном кремнии и SOI. Особый интерес представляет разновидность транзистора с двойным затвором – FinFET транзистора. В этом приборе тонкая кремниевая структура (столбик, вставка – fin) «обернуто» затвором. Выступающая передняя область тела – исток транзистора, выступающая задняя область – сток. Ток протекает в плоскости, параллельной плоскости структуры. Активная ширина прибора равна высоте столбика, и ее можно увеличивать путем параллельного включения многих столбиков. По своей топологии FinFET не отличается от традиционного МОП-транзистора, за исключением того, что активная область формируется вставками, а не представляет собой плоский прямоугольник. Появилась структура трехзатворного FinFET (рисунок 3).

Рис. 3. Структура FinFET: а) структура FinFET; б) FinFet SRAM

При переходе к 45 нм топологическим нормам для создания затворов транзисторов с малыми токами утечек использован новый материал для диэлектрика – так называемый high-k диэлектрик, в сочетании с новым материалом для электрода затвора транзистора на основе металлов.

Рассмотрим влияние различных технологических базисов на величину энергопотребления разработанного 5-разрядного таймера. Для сравнения выбраны технологии HCMOS-0.18μm, CMOS-0.35μm и AMS-0.6μm. Результаты представлены в таблице 1.

Таблица 1

Результаты расчета мощности таймера в различных тех. базисах

| Технология               | HCMOS 0.18<br>(Vdd=2v; L=0.18μm) | CMOS 0.35μm (Vdd=3.5V; Wn=0.8μ; Wp=3.2μ; Cn=3p; Vtn=0.6; Vtp=-0.6; Kn=200; Kp= 52; Tox=7) | AMS 0.6 (Vdd=5; Vtn=0.8; Vtp=-0.9; Kn=140; Kp=42; Wn=0.9; Wp=3) |

|--------------------------|----------------------------------|-------------------------------------------------------------------------------------------|-----------------------------------------------------------------|

| P <sub>inv</sub> , Вт    | 3,40E-07                         | 4,23E-06                                                                                  | 9,18E-06                                                        |

| P <sub>2and</sub> , Вт   | 4,64E-07                         | 5,07E-06                                                                                  | 1,13E-05                                                        |

| P <sub>3and</sub> , Вт   | 5,90E-07                         | 5,92E-06                                                                                  | 1,34E-05                                                        |

| P <sub>device</sub> , Вт | 9,71E-04                         | 3,56E-03                                                                                  | 7,41E-03                                                        |

#### *Снижение энергопотребления на схемотехническом уровне*

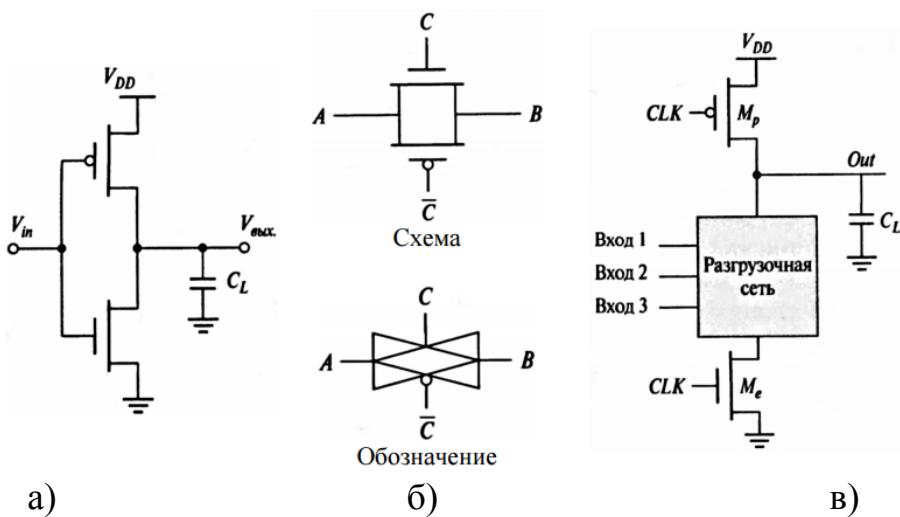

На схемотехническом уровне можно выделить несколько вариантов построения энергоэффективных решений: статическая КМОП логика, динамическая логика, логика на проходных транзисторах, адиабатическая логика, псевдо n-MOP логика, схемы с переменным пороговым напряжением, схемы с дополнительным источником питания, использование управления дополнительным затвором.

Рис. 4. Схемотехнические решения основных элементов: а) КМОП-инвертор; б) проходной вентиль; в) динамическая логика

Однако эффективного и универсального для всех приложений LP схемотехнического базиса в настоящее время не существует. Статическая КМОП-логика и логика на проходных транзисторах эффективны при построении комбинационных схем. Динамическая логика нашла применение при построении микропроцессоров.

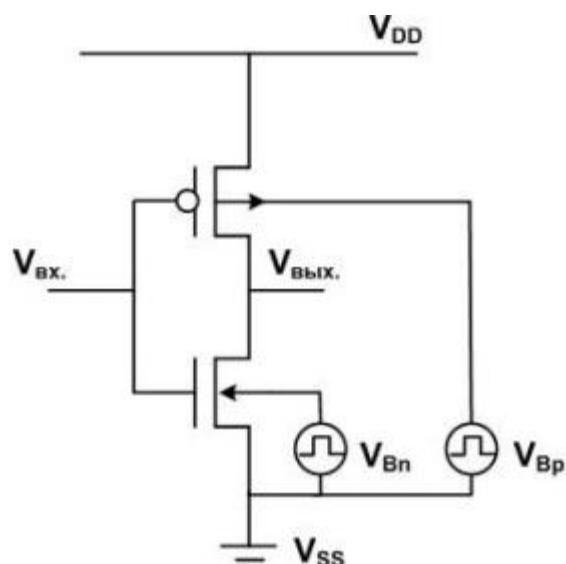

Использование элементов с изменяемым пороговым напряжением (VTCMOS) Технология VTCMOS используется в устройствах с низким пороговым напряжением. Используя эффект влияния подложки можно контролировать пороговое напряжение, что позволяет получить высокое  $V_{TH}$  в режиме ожидания и низкое  $V_{TH}$  в активном режиме для одного и того же транзистора. На рис. 5 приведена модификация электрической схемы КМОП-инвертора с применением технологии VTCMOS. Во время активного режима на подложку р-канального транзистора подается напряжение  $V_{DD}$ , а на подложку н-канального транзистора – 0V, обеспечивая низкое эффективное пороговое напряжение, и, следовательно, высокое быстродействие. Во время режима ожидания на подложку р- и н-канальных транзисторов подается напряжение  $2V_{DD}$  и  $-V_{DD}$  соответственно, эффективное пороговое напряжение увеличивается, уменьшая тем самым ток утечки. К недостаткам этой технологии можно отнести дополнительную схему управления смещением подложки.

Рис. 5. Технология VTCMOS

Чтобы оценить насколько возможно снижение энергопотребления, мы рассмотрим четыре стандартных элемента: Инвертор (INV), 2И-НЕ (NAND2) и 3И-НЕ (NAND3). В результате моделирования этих элементов были получены зависимости задержки и энергопотребления от напряжения питания (таблица 2).

Таблица 2. Зависимость энергопотребления от напряжения

| V <sub>dd</sub> , В | 2 В                 |         | 1.6 В               |         | 1.2 В               |         |

|---------------------|---------------------|---------|---------------------|---------|---------------------|---------|

|                     | t <sub>d</sub> , пс | P, мкВт | t <sub>d</sub> , пс | P, мкВт | t <sub>d</sub> , пс | P, мкВт |

| INV                 | 64                  | 0.34    | 73                  | 0.217   | 84.5                | 0.122   |

| NAND2               | 65.5                | 0.464   | 78                  | 0.296   | 89                  | 0.167   |

| NAND3               | 71.8                | 0.59    | 80                  | 0.377   | 95                  | 0.212   |

Снижение напряжения питания приводит к снижению энергопотребления элементов. Так для инвертора (INV) при снижении напряжения питания от 2 В до 1.2 В, энергопотребление снижается на 35.8%, для 2И-НЕ (NAND2) – 35.9% и для 3И-НЕ(NAND3) – 35.9%. Таким образом среднее снижение энергопотребления всех элементов составляет 35.9%, и уменьшение быстродействия на 30%.

### *Список литературы*

1. Угрюмов Е.П. Цифровая схемотехника. – СПб.: БХВ-Петербург, 2004.

2. Ракитин В.В. Интегральные схемы на КМОП-транзисторах: Учебное пособие. – М., 2007.

3. Физика полупроводниковых приборов: в 2-х кн. Кн. 1. / Пер. с англ. под ред. С. Зи. – М.: Мир, 1986.

4. Старосельский В.И. Физика полупроводниковых приборов микрэлектроники: уч. пособие. – М.: Высшее образование; Юрайт-Издат, 2009.