**Авторы:****Сибиряков Максим Андреевич**

канд. техн. наук, магистрант

**Сухих Андрей Владимирович**

канд. техн. наук, магистрант, аспирант

ФГБОУ ВО «Поволжский государственный

технологический университет»

г. Йошкар-Ола, Республика Марий Эл

## **РАЗРАБОТКА СТРУКТУРЫ КОММУТАТОРА PCI EXPRESS НА ОСНОВЕ СМО**

*Аннотация: в статье разработана модель коммутатора PCI Express на основе системы массового обслуживания (СМО) в среде моделирования и симуляции Simulink Matlab. Исследованы особенности работы основных блоков коммутатора. Определены основные характеристики работы моделируемой системы при обработке заявок (объем запоминающих устройств, пропускная способность, интенсивность поступления заявок на вход системы и др.).*

*Ключевые слова: Matlab, система массового обслуживания, Simulink, коммутатор, PCI Express.*

*Работа выполнена при поддержке гранта РФФИ: №16-37-00153 мол\_а.*

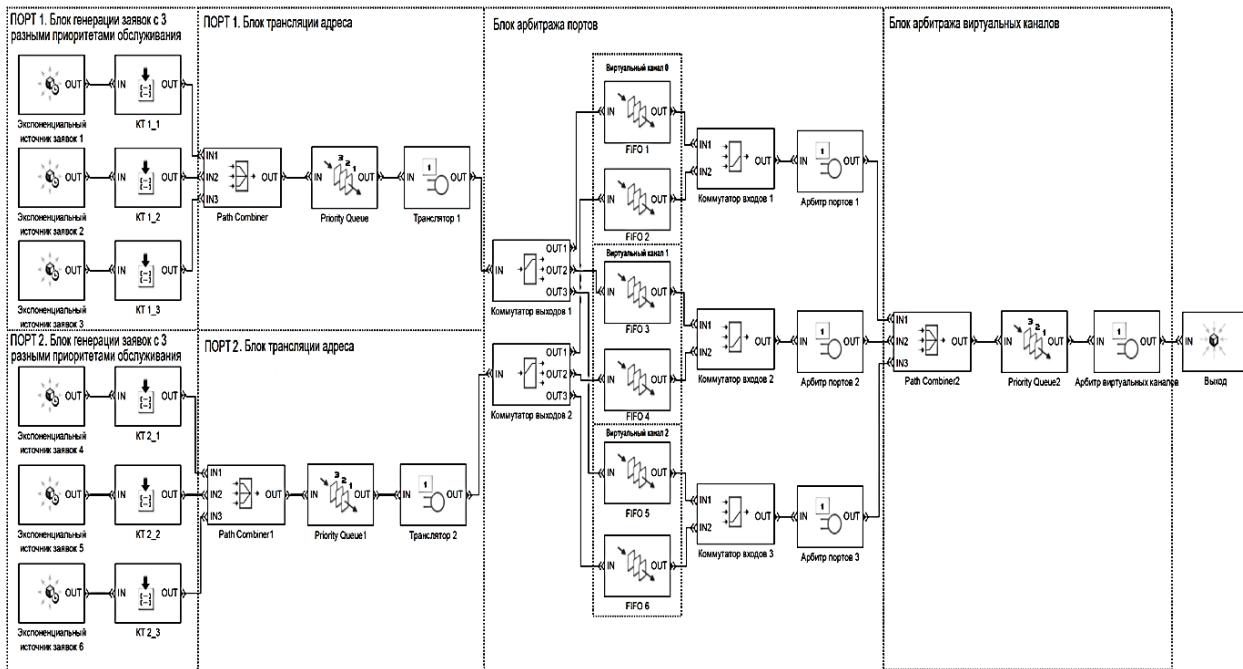

На рисунке 1 представлена СМО коммутатора PCI Express, созданная в среде Simulink Matlab. Система состоит из следующих компонентов:

### *Блоки генерации заявок*

На схеме присутствует два блока генерации заявок, которые моделируют поступление заявок на входные порты. Каждый блок содержит три «Экспоненциальных источника заявок», которые генерируют заявки в моменты времени, распределенные по экспоненциальному закону.

Все пришедшие заявки попадают в устройства, назначающие трафику приоритет путем присвоения специального числового атрибута в диапазоне от 1 до

3, где «1» – высший приоритет, «3» – низший. Предполагается, что заявки с низким приоритетом составляют основную массу и генерируются чаще, чем заявки с более высокими приоритетами.

Рис. 1. СМО коммутатора PCI Express, описывающая процессы трансляции и арбитража при передаче пакетов разного класса обслуживания с двух входных портов на один выходной, разработанная в среде SimuLink Matlab

### Блоки трансляции адреса

Сгенерированные заявки с разными приоритетами объединяются в единый поток и поступают в приоритетную очередь, которая пропускает заявки с приоритетом, начиная с высшего. Таким образом, заявки с высоким приоритетом проходят процедуру трансляции первыми.

### Блок арбитражса портов

В этом блоке два потока заявок с двух входных портов сортируются по очередям с помощью коммутаторов. В очередь «FIFO 1» попадают заявки с приоритетом «1» из первого порта, в «FIFO 2» – с приоритетом «1» из второго, в «FIFO 3» – с приоритетом «2» из первого порта и так далее. Группы очередей попарно

образуют «виртуальные каналы» в терминологии PCI Express. С каждого виртуального канала заявки попадают на «Арбитр портов». Арбитраж портов моделируется следующим образом: заявки с одинаковым приоритетом из двух очередей попадают на входы коммутатора, который передает их на устройство арбитража портов. Критерий, по которому коммутатор определяет с какого входного порта в данный момент будет передана заявка – равновероятный.

#### *Блок арбитража виртуальных каналов*

Прошедшие арбитраж портов заявки, поступают в единый канал передачи, приходят в приоритетную очередь. В арбитраже виртуальных каналов также имеют преимущество заявки с высоким приоритетом, пришедшие из «Виртуального канала 0».

С помощью разработанной модели можно проводить моделирование работы коммутатора. При изменении параметров интенсивности входящего потока заявок, поступающих на «Порт 1» и «Порт 2» из «Экспоненциальных источников заявок» и вариации времени обработки заявок в устройствах обслуживания в блоках трансляции, арбитража портов и виртуальных каналов, можно оценить следующие параметры системы:

- число заявок в любой из очередей (буферных элементах коммутатора) в текущий момент времени;

- среднее время пребывания заявок в любой очереди;

- среднюю длину любой очереди;

- число необслуженных заявок, например, из-за переполнения буфера;

- загруженность устройств обслуживания;

- оценивая количество поступивших заявок из источников и заявок, покинувших систему, можно оценить количество заявок, находящихся в системе одновременно.

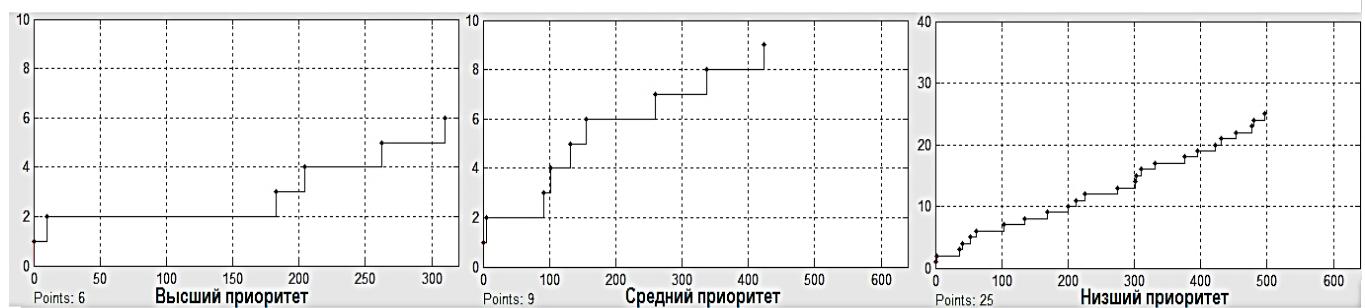

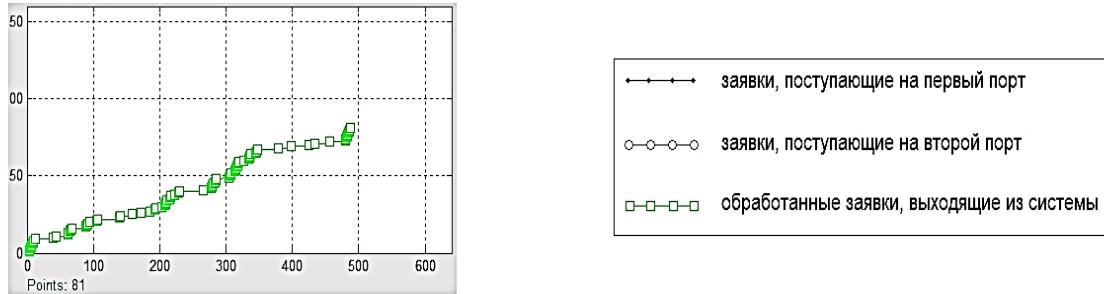

Например, на рисунке 2 показаны графики, отображающие число заявок в зависимости от времени, которые поступают и выходят из системы. Временной промежуток, в котором выполнялось моделирование, равен 500 единицам времени.

Число заявок с разным приоритетом обслуживания, поступающих на первый порт коммутатора

Число заявок с разным приоритетом обслуживания, поступающих на второй порт коммутатора

Число обработанных заявок, выходящих из системы

Рис. 2. Количество заявок, поступающих на входные порты

и выходящих из системы

Из диаграмм видно, какое количество заявок каждого приоритета поступило на входные порты и общее число заявок, покинувших систему. Для получения более точных значений, время моделирование может быть увеличено. Видно, что при заданных параметрах интенсивности входных источников и времени обработки заявок в узлах, на момент окончания времени моделирования в системе находятся 4 заявки.

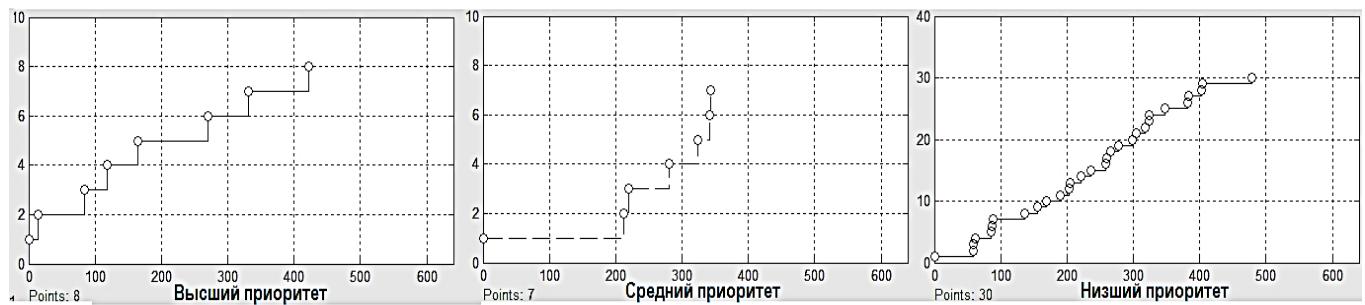

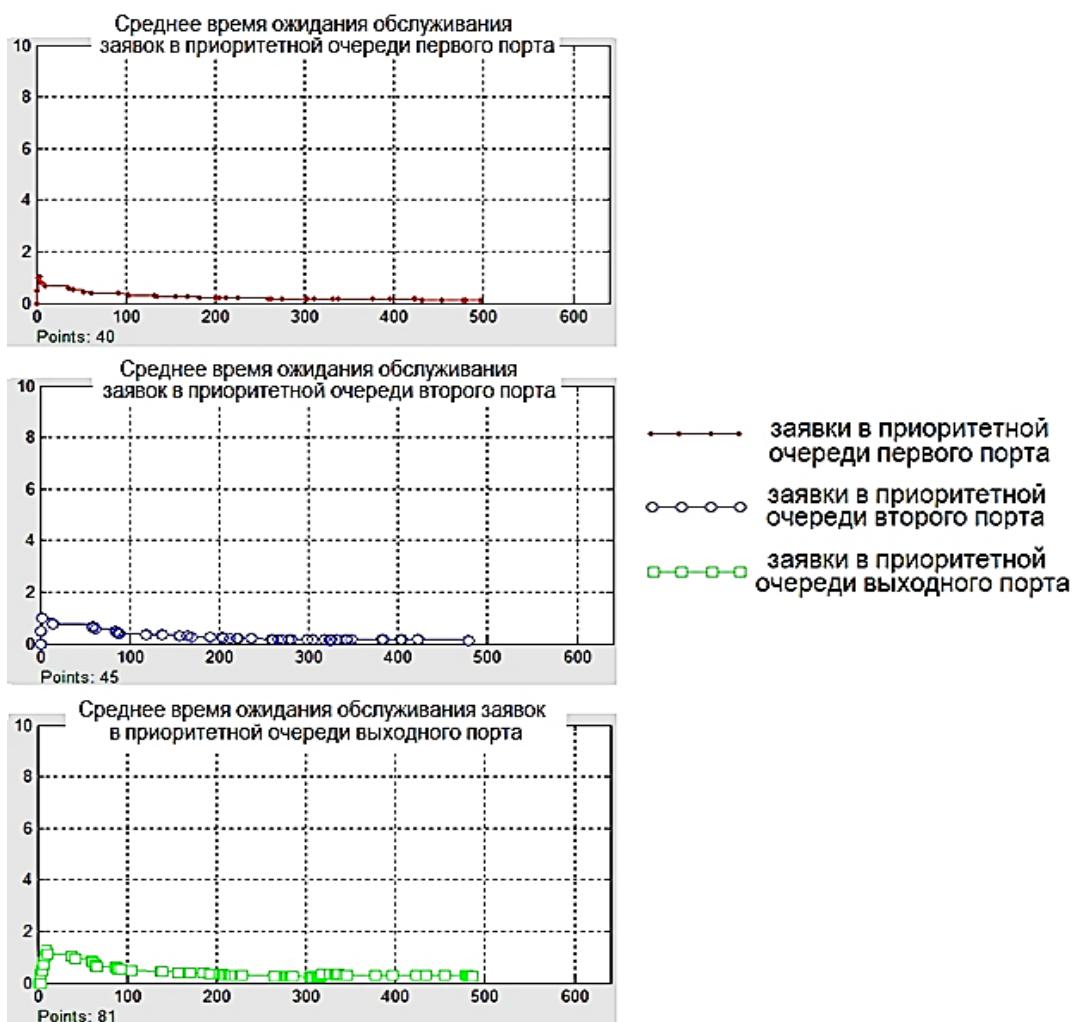

Рис. 3. Среднее время ожидания обслуживания заявок в приоритетных очередях портов коммутатора

На рисунке 3 показаны графики зависимости среднего времени ожидания обслуживания заявки в приоритетных очередях входящих и выходного портов. Как видно, при заданных интенсивностях входных потоков время ожидания заявок незначительно, что говорит о том, что коммутатор может обслуживать более интенсивные входные потоки, значения которых могут быть определены при дальнейших сериях испытаний модели коммутатора.

### **Список литературы**

1. Лацис А.О. Как построить и использовать суперкомпьютер. – М.: Бестселлер, 2003. – 240 с.

2. Сухих А.В. Организация межсистемной связи внутри вычислительного кластера на шине PCI Express / А.В. Сухих, Н.С. Васяева // Сборник материалов

Всероссийской научно-практической конференции с международным участием «Информационные технологии в профессиональной деятельности и научной работе»: В 2 ч. – Ч. 1. – Йошкар-Ола: ПГТУ, 2013. – С. 167–171.

3. Increase of productivity of the PCI Express switch for cluster systems / N.S. Vasjaeva, K.V. Ivanov, A.V. Suhih // In the World Scientific: Krasnoyarsk, Natural Technical Sciences. – 2014. – №10 (58). – P. 248–275.

4. PCI Express Base Specification. Revision 3.0 [Электронный ресурс]. – Режим доступа: <https://members.pcisig.com/wg/PCI-SIG/document/download/8269> (дата обращения: 10.02.2017).

5. Regula J. Using Non-transparent Bridging in PCI Express Systems. – PLX Technology, Inc. – 2004. – 31 с.